设计一个Verilog交通灯控制器是一个典型的数字设计问题。交通灯控制器需要管理多个方向的车流和行人信号,通常包括红灯、绿灯和黄灯。在设计时,我们需要考虑信号灯的变化规则以及如何根据这些规则来控制信号灯的状态。

下面是一个简单的交通灯控制器的Verilog代码示例。这个控制器将管理两个方向的交通(例如,东西向和南北向),每个方向都有红灯、绿灯和黄灯。控制器的状态转换将基于一个简单的计时器,以确保每个方向有足够的时间来处理交通流。

```verilogmodule traffic_light_controller light_EW, // 东西向信号灯 output reg light_NS // 南北向信号灯qwe2;

// 定义状态localparam RED = 3'b00, YELLOW = 3'b01, GREEN = 3'b10;

// 定义计时器reg timer;reg state_EW, state_NS; // 东西向和南北向的状态reg timer_EW, timer_NS; // 东西向和南北向的计时器

// 状态转换逻辑always @ begin if begin // 初始化状态和计时器 state_EW if begin // 南北向计时结束,切换到下一个状态 case RED: begin state_NS // 状态输出逻辑always @ begin // 东西向信号灯 case RED: light_EW // 南北向信号灯 case RED: light_NS endmodule```

这个代码示例创建了一个简单的交通灯控制器,它使用两个状态机来管理东西向和南北向的交通灯。每个状态机都有一个计时器,用于确定何时切换到下一个状态。在这个例子中,每个状态持续大约5秒(假设时钟频率为50MHz)。

请注意,这个代码只是一个基本示例,实际的交通灯控制器可能需要更复杂的逻辑来处理不同的交通情况和紧急情况。此外,这个控制器没有考虑行人信号和车辆检测器,这些在实际的交通灯控制系统中也是重要的组成部分。

基于Verilog的交通灯控制器设计:原理与实现

随着城市化进程的加快,交通流量日益增大,交通灯控制系统的设计显得尤为重要。本文将详细介绍基于Verilog的交通灯控制器设计,包括设计原理、实现方法以及仿真验证过程。

一、设计背景与意义

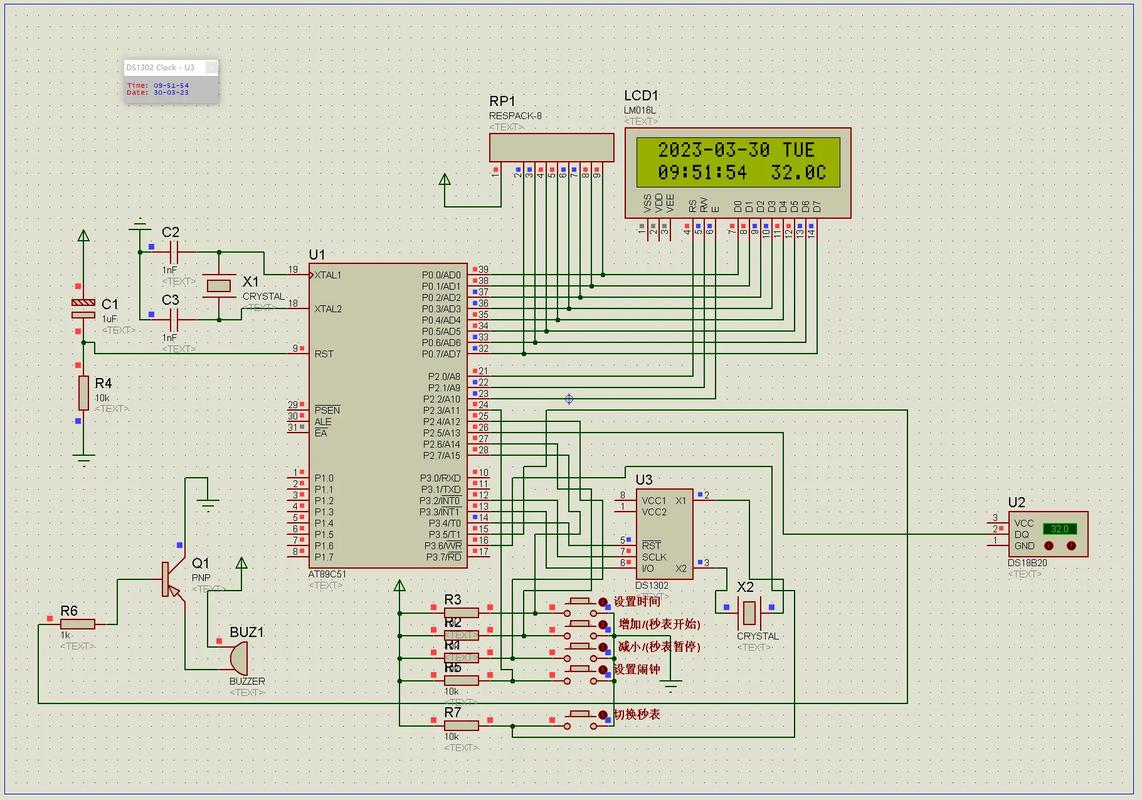

交通灯控制器是城市交通管理的重要组成部分,其设计直接关系到交通效率和交通安全。传统的交通灯控制器多采用单片机或PLC等硬件实现,但存在调试困难、扩展性差等问题。而基于Verilog的交通灯控制器设计,利用FPGA等可编程逻辑器件,具有设计灵活、易于调试、扩展性强等优点。

二、设计原理

基于Verilog的交通灯控制器设计主要涉及以下几个模块:

时钟模块:产生系统时钟信号,用于控制各个模块的运行。

状态机模块:根据输入信号和预设的时序,控制交通灯的转换。

信号灯控制模块:根据状态机模块的输出,控制红、黄、绿三种信号灯的亮灭。

数码管显示模块:显示交通灯的倒计时时间。

设计原理如下:

时钟模块产生1Hz的时钟信号,用于控制整个系统的运行。

状态机模块根据预设的时序,控制交通灯的转换。例如,东西方向绿灯亮60秒,黄灯亮5秒,红灯亮45秒;南北方向绿灯亮45秒,黄灯亮5秒,红灯亮60秒。

信号灯控制模块根据状态机模块的输出,控制红、黄、绿三种信号灯的亮灭。

数码管显示模块显示交通灯的倒计时时间,方便驾驶员和行人了解交通灯的剩余时间。

三、实现方法

基于Verilog的交通灯控制器设计主要采用以下方法:

使用Verilog HDL语言进行模块设计,包括时钟模块、状态机模块、信号灯控制模块和数码管显示模块。

利用FPGA开发板进行硬件实现,如Xilinx或Altera等。

将设计下载到FPGA开发板,进行实际运行测试。

以下是部分Verilog代码示例:

module traffic_light_controller(

input clk, // 系统时钟

input reset, // 复位信号

output reg [1:0] red_green, // 红绿灯信号

output reg [3:0] count // 数码管显示

// 时钟分频模块

always @(posedge clk or posedge reset) begin

if (reset) begin

count

四、仿真验证

使用仿真软件对设计进行功能验证,确保设计符合预期。以下是仿真结果截图: