当然可以。Verilog是一种硬件描述语言,常用于数字电路设计。下面是一个简单的Verilog计数器代码示例:

```verilogmodule counter out // 4位计数器输出qwe2;

always @ begin if begin out endmodule```

这个计数器模块有三个端口:`clk` 是时钟输入,`reset` 是复位输入,`out` 是4位宽的输出,表示计数器的当前值。每当`clk`的上升沿到来时,如果`reset`不是高电平,计数器的值就会增加1。如果`reset`是高电平,计数器的值会被重置为0。

请注意,这个计数器是递增的,并且没有溢出检测。在实际应用中,你可能需要根据具体需求对代码进行修改。

深入浅出Verilog计数器代码编写指南

在数字电路设计中,计数器是一个基础且重要的组件。它能够对输入的时钟信号进行计数,并在达到特定值时产生输出信号。Verilog作为一种硬件描述语言,被广泛应用于FPGA和ASIC的设计中。本文将深入浅出地介绍如何使用Verilog编写计数器代码。

一、计数器的基本概念

计数器是一种能够对输入信号进行计数的数字电路。它通常由一系列触发器组成,每个触发器存储一个二进制位。计数器的输出通常是一个或多个触发器的状态,表示计数器的当前值。

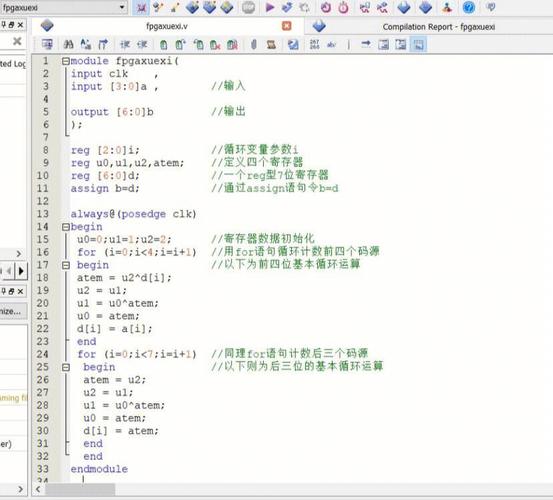

二、Verilog计数器的基本结构

在Verilog中,计数器通常由以下部分组成:

输入端口:包括时钟信号(clk)、复位信号(reset)和使能信号(enable)。

输出端口:通常是一个寄存器,表示计数器的当前值。

内部逻辑:根据输入信号和计数器的当前值,决定计数器的下一个状态。

三、Verilog计数器代码编写示例

以下是一个简单的4位二进制计数器的Verilog代码示例:

```verilog

module counter (

input wire clk, // 时钟信号

input wire reset, // 复位信号

input wire enable, // 使能信号

output reg [3:0] count // 计数输出

always @(posedge clk or negedge reset) begin

if (!reset) begin

定时器:根据输入的时钟信号,计数器可以用来实现定时功能。

分频器:通过计数器对时钟信号进行分频,可以得到不同频率的时钟信号。

序列发生器:计数器可以用来产生一系列有序的信号,如地址信号、控制信号等。

五、Verilog计数器代码优化技巧

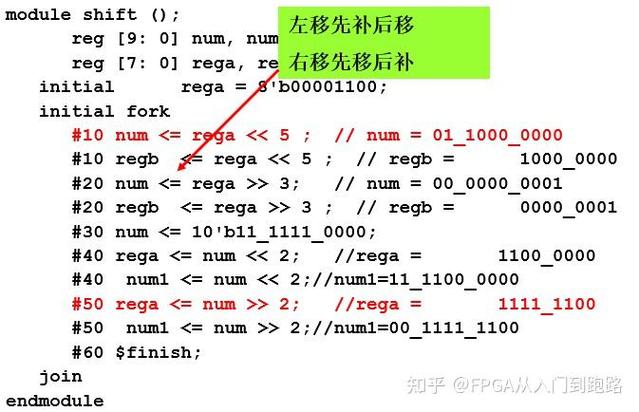

使用非阻塞赋值语句:在always块中,使用非阻塞赋值语句可以避免竞争条件。

使用case语句:当计数器的下一个状态取决于当前状态时,使用case语句可以提高代码的可读性。

使用generate语句:当需要生成多个计数器实例时,使用generate语句可以提高代码的复用性。

Verilog计数器是数字电路设计中的基础组件。通过本文的介绍,相信读者已经对Verilog计数器代码的编写有了初步的了解。在实际应用中,根据不同的需求,可以对计数器进行扩展和优化,以满足各种场景的需求。