在Verilog中,创建一个计数器是数字设计中的一个基本任务。下面是一个简单的Verilog代码示例,展示了如何创建一个基本的计数器。这个计数器在时钟信号(clk)的上升沿递增,并具有一个复位信号(rst),当复位信号为高时,计数器将重置为0。

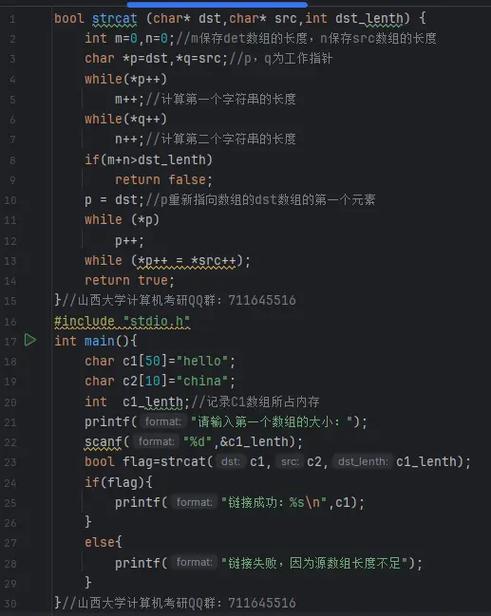

```verilogmodule counter count // 8位计数器qwe2;

always @ begin if begin count endmodule```

在这个代码中,我们定义了一个名为`counter`的模块,它接受一个时钟信号`clk`和一个复位信号`rst`,并输出一个8位的计数器`count`。计数器的值在时钟的每个上升沿递增,除非复位信号为高,在这种情况下,计数器会重置为0。

请注意,这个计数器是无限循环的,它不会停止递增,除非复位信号被激活。如果你需要一个有限计数器,你可以添加一个额外的输入来定义计数器的最大值,并在达到这个值时停止递增或执行其他操作。

深入浅出Verilog计数器设计

在数字电路设计中,计数器是一种基本的电路组件,用于对输入信号进行计数。Verilog作为一种硬件描述语言,被广泛应用于数字电路的设计与仿真。本文将深入浅出地介绍Verilog计数器的原理、设计方法以及在实际应用中的注意事项。

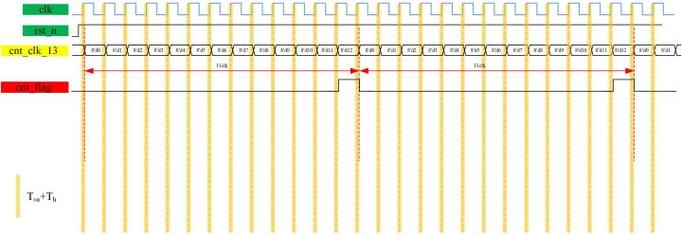

一、Verilog计数器的基本原理

Verilog计数器是一种基于时钟信号的计数电路,它能够对输入的时钟脉冲进行计数。计数器的核心是一个或多个触发器,这些触发器按照一定的逻辑关系组合起来,形成计数器的计数功能。

二、Verilog计数器的设计方法

1. 同步计数器设计

同步计数器是指计数器的所有触发器都由同一个时钟信号触发。同步计数器的设计方法如下:

确定计数器的位数:根据所需的计数范围确定计数器的位数。

选择触发器类型:常用的触发器类型有D触发器、JK触发器等。

设计计数逻辑:根据触发器类型和计数要求,设计计数逻辑电路。

编写Verilog代码:使用Verilog语言描述计数逻辑电路。

2. 异步计数器设计

异步计数器是指计数器的各个触发器由不同的时钟信号触发。异步计数器的设计方法如下:

确定计数器的位数:与同步计数器相同。

选择触发器类型:与同步计数器相同。

设计计数逻辑:根据触发器类型和计数要求,设计计数逻辑电路。

编写Verilog代码:使用Verilog语言描述计数逻辑电路,并考虑时钟域交叉问题。

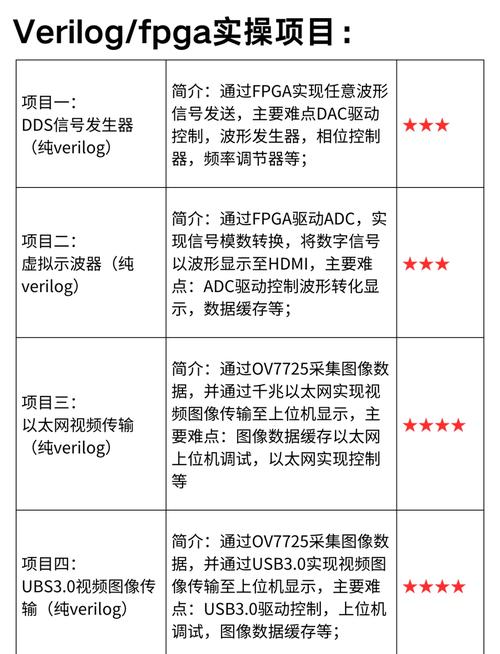

三、Verilog计数器的应用实例

以下是一个使用Verilog语言设计的4位同步计数器的实例:

```verilog

module sync_counter(

input clk, // 时钟信号

input reset, // 复位信号

output reg[3:0] count // 计数输出

always @(posedge clk or negedge reset) begin

if (!reset)

count 1. 时钟域交叉问题:在异步计数器设计中,需要考虑时钟域交叉问题,避免由于时钟不同步导致的错误。

2. 触发器翻转问题:在计数器设计中,需要注意触发器的翻转问题,确保计数器能够正确计数。

3. 代码可读性:在编写Verilog代码时,应注意代码的可读性,便于后续的调试和维护。

Verilog计数器是数字电路设计中常用的基本组件,掌握Verilog计数器的设计方法对于数字电路设计人员来说至关重要。本文从基本原理、设计方法、应用实例以及注意事项等方面对Verilog计数器进行了详细介绍,希望对读者有所帮助。