Verilog 是一种硬件描述语言,用于数字电路的设计和仿真。它允许设计者以文本形式描述电路的行为和结构,然后使用仿真工具来验证设计是否符合预期。Verilog 的设计可以在不同的抽象级别进行,从行为级到结构级,再到门级。

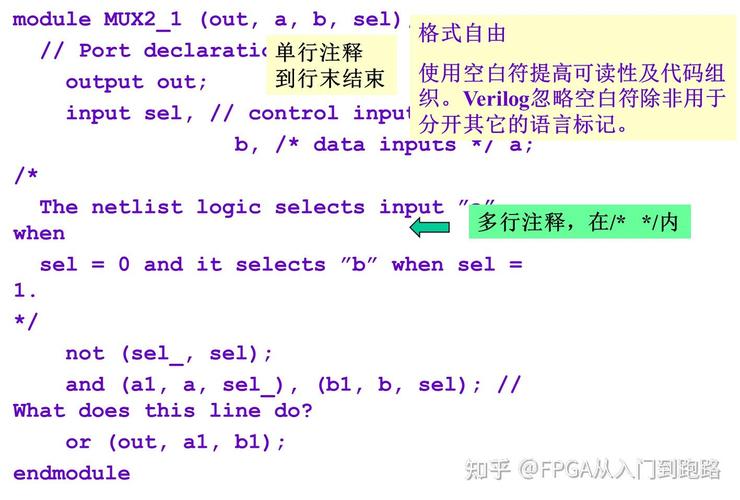

在 Verilog 中,设计通常包括模块(module)的定义,其中包含输入、输出和内部信号。模块之间可以相互连接,形成更大的系统。Verilog 提供了丰富的语法和结构,包括条件语句、循环、过程块、任务和函数等,用于描述电路的行为。

Verilog 还支持时间控制,允许设计者指定信号的变化时间和顺序。这有助于仿真工具准确模拟电路的时序行为。此外,Verilog 还支持测试平台(testbench)的编写,用于生成输入信号并观察电路的输出响应。

总的来说,Verilog 是一种强大的工具,用于数字电路的设计、仿真和验证。它提供了灵活的语法和结构,支持不同级别的抽象,并且与仿真工具紧密集成,使得电路设计变得更加高效和可靠。

深入浅出Verilog:FPGA开发中的硬件描述语言

一、Verilog简介

Verilog是一种硬件描述语言(HDL),主要用于数字电路设计和FPGA(现场可编程门阵列)开发。它允许工程师以文本形式描述电路的行为、结构和数据流,从而实现电路的功能。

二、Verilog的基本语法

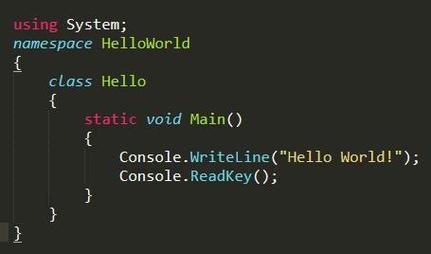

关键字:Verilog中的关键字都是小写的,如module、reg、wire等。

数据类型:Verilog支持多种数据类型,包括整数、实数、逻辑等。

运算符:Verilog支持算术运算符、逻辑运算符和位运算符等。

模块:模块是Verilog中的基本单元,用于描述电路的功能。

三、Verilog模块设计

Verilog模块是描述电路功能的基本单元。以下是一个简单的Verilog模块示例:

```verilog

module adder(

input wire a,

input wire b,

output wire sum

assign sum = a ^ b;

endmodule

在这个示例中,`adder`模块是一个简单的加法器,它有两个输入`a`和`b`,以及一个输出`sum`。模块内部使用异或运算符`^`来实现加法功能。

四、Verilog的时序控制

always块:用于描述电路的时序行为,可以包含敏感列表和过程语句。

initial块:用于初始化电路的初始状态,只执行一次。

always_comb和always_ff:用于描述组合逻辑和时序逻辑。

五、Verilog的测试平台

测试平台是验证Verilog设计正确性的重要工具。以下是一个简单的测试平台示例:

```verilog

module testbench;

reg a;

reg b;

wire sum;

adder uut (

.a(a),

.b(b),

.sum(sum)

);

initial begin

a = 0;

b = 0;

10;

a = 1;

b = 1;

10;

a = 0;

b = 1;

10;

$finish;

end

endmodule

在这个测试平台中,我们创建了一个`adder`模块的实例,并通过改变输入信号`a`和`b`的值来验证加法器的功能。

六、Verilog的优化技巧

使用寄存器:寄存器可以存储中间结果,提高电路的运行速度。

避免组合逻辑环:组合逻辑环会导致电路性能下降,应尽量避免。

使用时钟域交叉技术:时钟域交叉技术可以解决不同时钟域之间的同步问题。

Verilog是一种强大的硬件描述语言,在FPGA开发中发挥着重要作用。通过掌握Verilog的基本语法、模块设计、时序控制和测试平台等知识,工程师可以轻松地实现各种数字电路功能。本文对Verilog进行了简要介绍,希望对读者有所帮助。