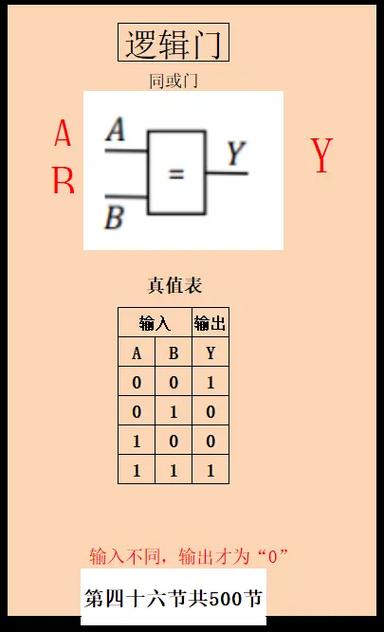

在Verilog中,异或运算可以通过使用`^`符号来实现。异或运算的结果是当两个输入位不同时为1,相同时为0。下面是一个简单的Verilog模块示例,展示了如何使用异或运算:

```verilogmodule xor_example ;

assign y = a ^ b;

endmodule```

在这个例子中,`xor_example`模块有两个输入`a`和`b`,以及一个输出`y`。输出`y`是`a`和`b`的异或结果。当`a`和`b`的值不同时,`y`为1;当`a`和`b`的值相同时,`y`为0。

深入解析Verilog中的异或操作

在数字电路设计中,异或(XOR)操作是一种基本的逻辑运算,用于比较两个二进制位是否不同。Verilog作为一种硬件描述语言,提供了丰富的逻辑运算符来支持这种操作。本文将深入探讨Verilog中的异或操作,包括其基本用法、实现方式以及在实际设计中的应用。

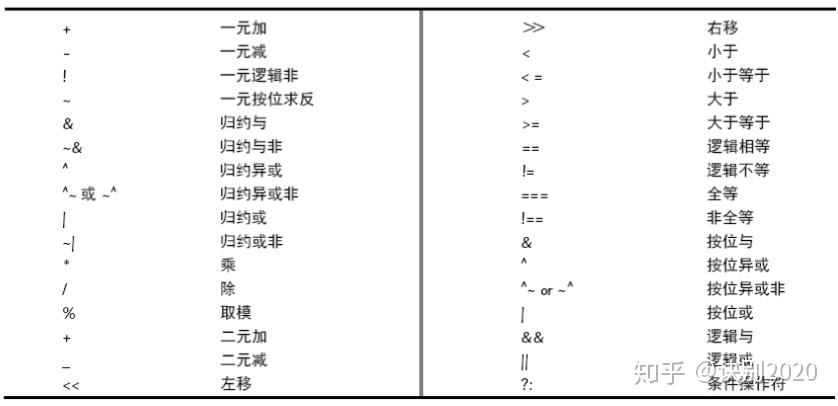

一、Verilog中的异或运算符

在Verilog中,异或运算符用符号“^”表示。它可以直接应用于两个二进制数,返回一个结果,该结果为1当且仅当两个输入位不同,否则为0。

二、异或运算符的语法

以下是一个简单的异或运算符的例子:

```verilog

module xor_example (

input a,

input b,

output y

assign y = a ^ b;

endmodule

在这个例子中,`a`和`b`是两个输入信号,`y`是输出信号。当`a`和`b`的值不同(一个为1,另一个为0)时,`y`的值将为1;如果它们相同,`y`的值将为0。

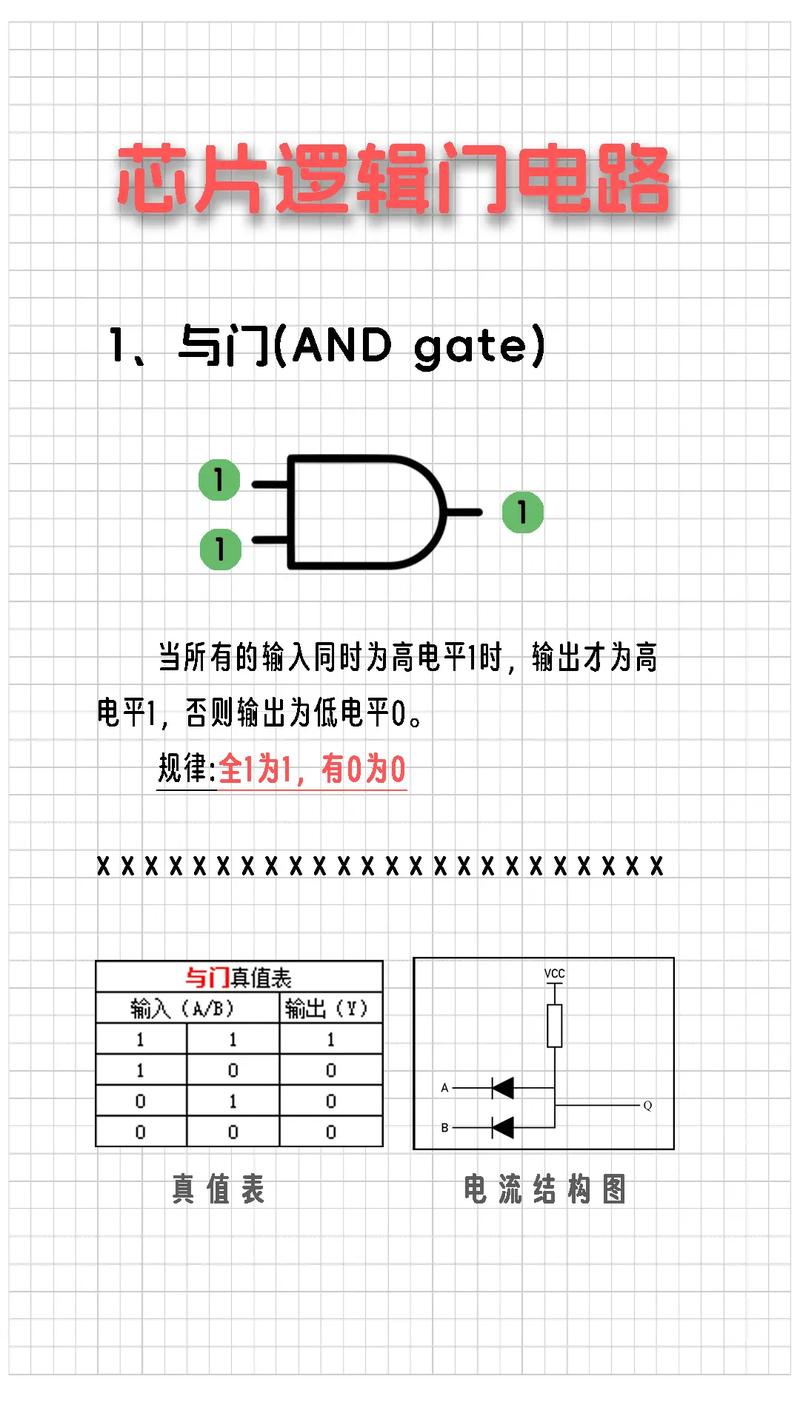

三、异或运算的实现方式

1. 逻辑门实现

异或运算可以通过两个与门(AND)和一个或门(OR)的组合来实现。以下是使用逻辑门实现的异或运算的Verilog代码:

```verilog

module xor_gate (

input a,

input b,

output y

wire w1, w2;

assign w1 = a