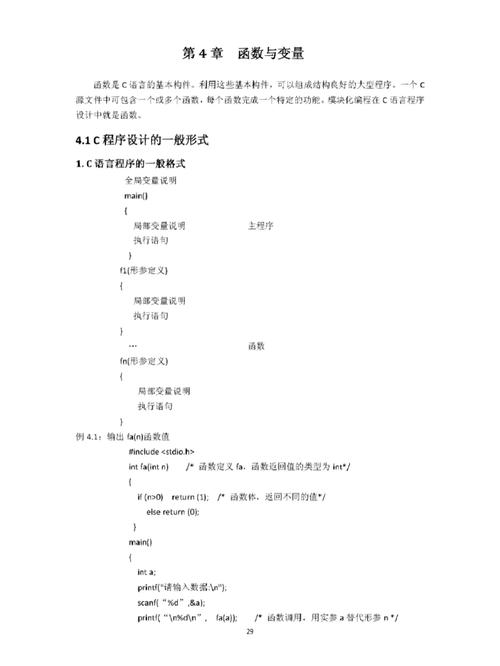

D触发器(Data Trigger)是一种基本的数字电路组件,它用于存储一位二进制信息。在Verilog中,我们可以使用以下代码来定义一个D触发器:

```verilogmodule d_flip_flop;

// 异步复位逻辑 always @ begin if q endmodule```

这段代码定义了一个名为 `d_flip_flop` 的模块,它接受三个输入:`clk`(时钟信号)、`d`(数据输入)和`reset`(异步复位信号),以及一个输出 `q`。在时钟信号的上升沿或者复位信号的上升沿,触发器会根据 `d` 的值更新 `q` 的值。如果复位信号为高,`q` 将被设置为0。

请注意,这个D触发器是一个基本的示例,它没有包含任何时序检查或综合约束。在实际的FPGA或ASIC设计中,可能需要添加额外的时序约束来确保设计的时序性能。

在数字电路设计中,触发器是基本且重要的组成部分。D触发器(D Flip-Flop)作为一种基础的时序逻辑元件,广泛应用于各种数字系统中。本文将详细介绍D触发器的Verilog实现,包括其基本原理、结构以及Verilog代码编写方法。

D触发器的基本原理

D触发器是一种具有两个稳定状态的时序逻辑电路,其输出状态仅取决于当前的输入状态和时钟信号。D触发器具有以下特点:

具有一个数据输入端(D),一个时钟输入端(CLK),一个复位端(RSTN)和一个输出端(Q)。

在时钟信号的上升沿或下降沿,根据输入端D的状态改变输出端Q的状态。

复位端RSTN用于将输出端Q置为0或1,通常为低电平有效。

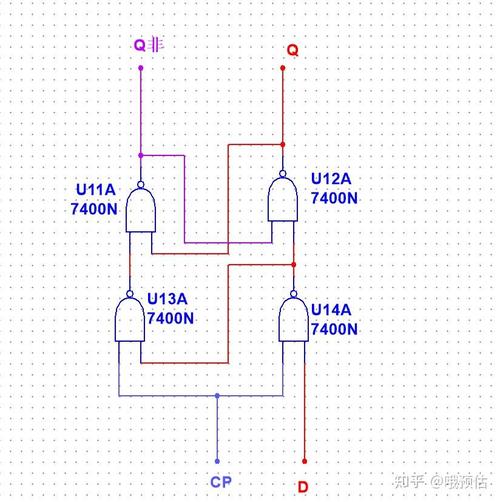

D触发器的结构

D触发器主要由一个D触发器单元和两个与非门组成。D触发器单元负责根据时钟信号和输入端D的状态改变输出端Q的状态,两个与非门分别用于实现时钟信号的上升沿触发和下降沿触发。

以下是一个D触发器的结构图: